공유하기

외계인의 기술력? 프로세서 미세공정과 아키텍처

- 동아닷컴

-

입력 2018년 12월 11일 11시 09분

글자크기 설정

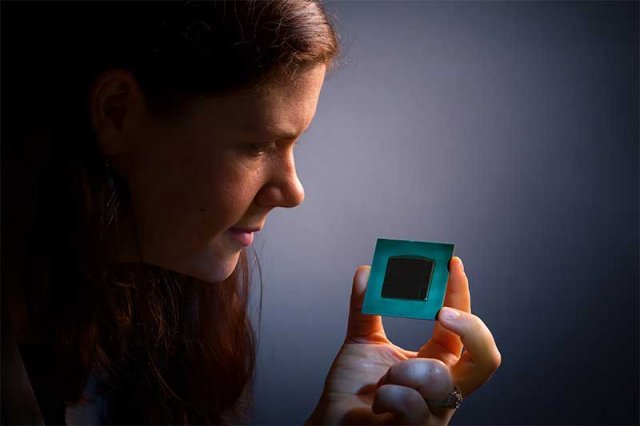

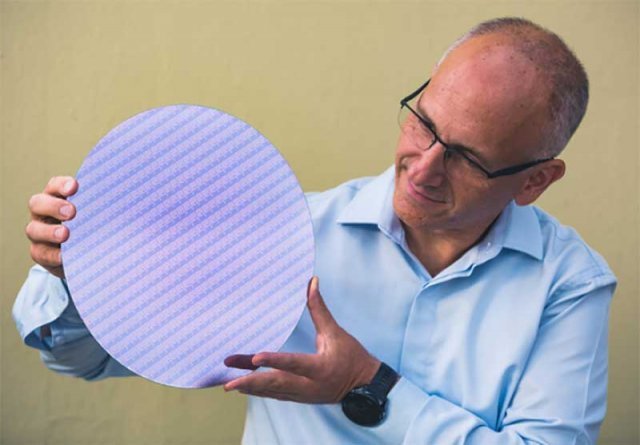

일반적으로 공정을 미세화하면 전력 소모가 줄고 발열이 낮아지며, 이를 바탕으로 코어를 늘리거나 클럭을 높여 기존과 전력 소모가 같으면서 성능을 더 높은 프로세서를 내놓을 수 있다. 공정 미세화를 통해 같은 부피의 프로세서 안에 더 많은 기능을 넣을 수 있는 것은 물론, 트랜지스터의 크기가 작아지면서 전압이 낮아지고 결과적으로는 전력 소모도 줄어들기 때문이다. 프로세서로 유입되는 전압이 낮아지면 당연히 발열도 줄어들고, 이를 냉각시키기 위한 냉각장치 역시 더 적은 전력으로 작동한다.

사실 프로세서의 성능을 올리는 방법은 간단하다. 공정을 미세화 하지 않더라도, 물리적인 크기를 키우면 이전보다 두 배, 네 배씩 성능을 강화할 수 있다. 그렇다면 제조사는 왜 이러한 방식 대신, 공정 미세화를 통해 집적도를 높일까? 바로 효율성 때문이다.

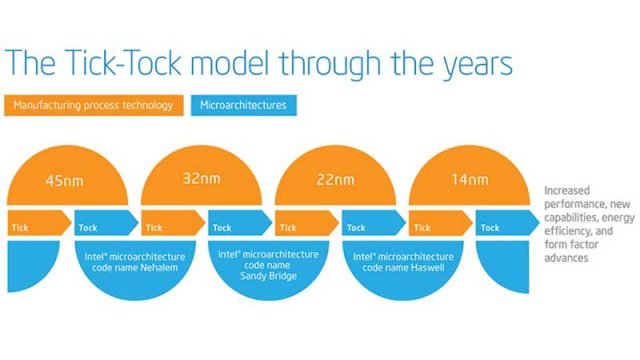

이 때문에 인텔 등 세계적인 반도체 기업은 제품 로드맵을 통해 공정 개선 계획을 공개하며 기술력을 강조한다. 인텔의 틱톡 전략이 이러한 사례다. 틱톡 전략이란 새로운 프로세서를 내놓을 때마다 공정 미세화(틱), 아키텍처 개선(톡)을 반복하는 것이다. 예를 들어 틱 전략에 해당하는 아이비브릿지는 22나노 공정을 도입하고, 4세대인 하스웰은 톡 전략을 통해 아키텍처를 개선했다. 다시 5세대인 브로드웰은 14나노 공정을 도입했고, 6세대 스카이레이크에서는 아키텍처를 개선했다.

물론 인텔은 14나노를 도입한 이후 공정 미세화에 난항을 겪으며 기존의 틱톡 전략을 약간 선회한 PAO 전략을 도입했다. 공정 개선과 아키텍처 개선을 반복하는 틱톡과 달리, PAO는 공정 개선(P) -> 아키텍처 개선(A) -> 최적화(O)의 단계로 이어지는 프로세서 전략이다. 7세대인 카비레이크는 공정 개선(5세대), 아키텍처 개선(6세대)에 이어 최적화 단계의 프로세서로, 6세대와 비교하면 전력 소모는 동일하지만, 기본 연산 속도는 0.2GHz 빠르게, 가속 시 속도는 0.5GHz 더 빠르게 작동한다.

하지만 인텔의 계획과는 달리, 7세대 이후 오늘날 9세대 프로세서까지 14나노 공정을 이어가고 있다. 같은 시기, 경쟁사에서는 이미 10나노 공정을 발표했고, 나아가 최근에는 7나노 공정 프로세서 출시 계획까지 발표한 만큼, 공정 미세화에서 인텔이 뒤쳐지는 듯한 느낌도 준다.

공정 미세화는 엄밀히 말해 프로세서 성능과 직접적인 관련은 적다. 앞서 말한 것처럼 저항을 낮춰 발열을 줄이고, 이에 따라 냉각에 필요한 전력 소모도 줄어든다. 즉, 공정 미세화는 발열 관리나 집적도 향상에 더 높은 관련이 있으며, 이는 전압을 높이거나 코어 수를 늘릴 수 있는 기초가 된다.

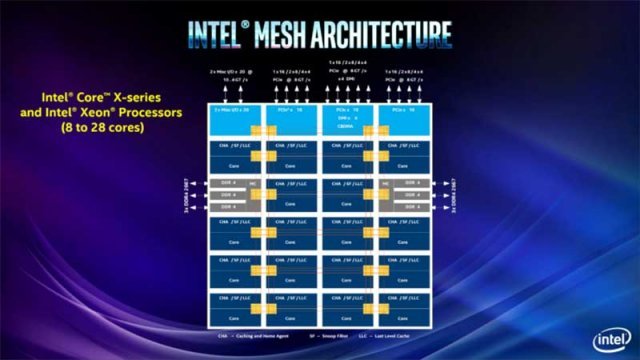

프로세서의 성능에는 이러한 공정 미세화보다는 아키텍처가 직접적인 영향을 준다. 아키텍처란 쉽게 말해 데이터를 처리하는 방식을 말하며, 아키텍처를 개선한다는 말은 데이터 처리 방식의 효율성을 높이고, 이를 통해 성능을 높인다는 의미다. 실제로 14나노 공정으로 제작한 인텔 8세대 코어 i5 프로세서(6코어 6스레드)는 14나노 공정으로 제작한 동급의 경쟁사 프로세서(6코어 12스레드)보다 코어 수는 적지만, 게임을 실행할 때 더 높은 성능을 보이기도 했다. 물론 가격적인 측면에서는 경쟁사가

정리하자면, 인텔은 최근 선보인 9세대 까지 표면상으로는 14나노 공정을 유지했지만, 내부적으로는 14나노+, 14나노++ 등으로 같은 공정 안에서 최적화를 이뤘다. 뿐만 아니라 타사의 14나노 공정과 비교하면 트랜지스터 집적도가 최대 1.5배 높아, 타사의 동급 제품보다 체감 성능이 더 높은 경우도 많았다. 내년부터 출시를 예고한 10나노 공정이 본격적으로 자리 잡으면, 이미 시장에서 경쟁사들이 선보인 7나노 공정의 제품과도 경쟁할 수 있을 전망이다.

-

- 좋아요

- 0개

-

- 슬퍼요

- 0개

-

- 화나요

- 0개

![보일러 풀가동해도 춥다?…난방비 폭탄 범인은 ‘이것’ [알쓸톡]](https://dimg.donga.com/a/464/260/95/1/wps/NEWS/FEED/Donga_Home_News2/133029050.5.thumb.png)

댓글 0