공유하기

반도체 용량 1000배 높일 트랜지스터 개발

-

입력 2000년 12월 7일 18시 48분

글자크기 설정

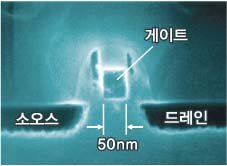

7일 한국과학기술원 전자전산학과 신형철 교수팀은 트랜지스터에서 전자를 공급하는 곳인 ‘소스’와 전자를 회수하는 ‘드레인’의 끝 부분 두께를 현재의 30㎚(나노미터·1㎚〓10억분의1m)에서 2㎚로 획기적으로 줄이는 방법을 개발했다.

이에 따라 전기신호를 전달하고 제어하는 게이트의 두께도 현재 180㎚(1기가D램)에서 50㎚로 크게 줄어들게 됐다. 50㎚는 머리카락 두께의 2000분의1에 해당한다.

반도체 칩은 트랜지스터를 모아놓은 것으로 트랜지스터 크기가 줄어들면 같은 면적에 많은 트랜지스터를 심을 수 있어 반도체의 기억용량이 크게 늘어난다.

신교수는 “전기적으로 유도된 전자층을 이용해 소스와 드레인의 두께를 줄이는 방식으로 트랜지스터 크기를 축소시킬 수 있었다”고 말했다.

신교수는 “앞으로는 두께 20㎚의 게이트 개발에 도전할 계획”이라며 “이 프로젝트가 성공하면 현재 D램 분야의 주력제품인 64MD램의 1만6000배의 정보를 담을 수 있는 테라급 반도체와 하나의 칩 위에 여러 기능을 합친 시스템 온 칩(System on Chip) 등의 개발이 실현될 것”이라고 예상했다.

연구자들은 이 기술에 대해 미국 등 주요 국가에 특허를 출원했고 상용화 연구는 지난해 1기가D램을 세계 최초로 선보였던 삼성전자가 맡기로 했다.

<강석기 동아사이언스기자>alchimiste@donga.com

-

- 좋아요

- 0개

-

- 슬퍼요

- 0개

-

- 화나요

- 0개