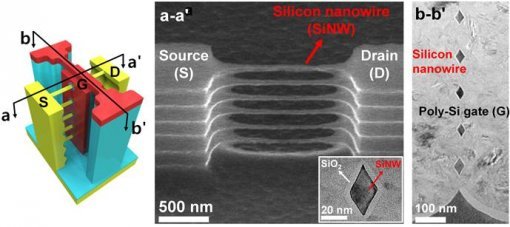

KAIST 전기 및 전자공학부 이병현 박사과정 연구원은 나노종합기술원 기술진과 공동으로 실리콘 기반 5단 수직 적층 반도체 트랜지스터 개발에 성공했다고 23일 밝혔다.

반도체 트랜지스터는 각종 반도체 칩을 만드는 기본소자로 모든 전자기기의 핵심 구성요소다. 더 작고 성능 좋은 반도체를 만들기 위해 세계적으로 치열한 소형화 경쟁이 벌어지고 있다.

이 연구원 팀은 기존 실리콘 트랜지스터를 차근차근 쌓지 않고 한 번에 찍어내는 방식을 개발해 이 문제를 해결했다. 이렇게 개발한 5단 적층 실리콘 나노선 채널을 보유한 반도체 트랜지스터는 흔히 유통되고 있는 1층 구조 단일 나노선 기반의 트랜지스터보다 5배의 향상된 성능을 보였다.

연구진은 이번 성과가 기술적 한계에 부딪힌 반도체 트랜지스터 분야에 새로운 돌파구를 제시할 것으로 기대하고 있다.

이 연구원은 “일괄 플라스마 건식 식각 공정이란 방식을 적용한 결과 새로운 트랜지스터 제조공법을 확보했다”며 “여러 층의 반도체를 쌓아 올리던 기존 적층식 구조에 비해 제작비용이 크게 낮아질 걸로 기대된다”고 말했다.

대전=전승민 동아사이언스 기자 enhanced@donga.com

-

- 좋아요

- 0개

-

- 슬퍼요

- 0개

-

- 화나요

- 0개

-

- 추천해요

- 개

지금 뜨는 뉴스

-

“개저씨들이 나 죽이려고”…민희진 막말 토로에 얼굴 감싼 변호사

- 좋아요 개

- 코멘트 개

-

전립선암 예방? “남자 ‘손’에 달렸다”

- 좋아요 개

- 코멘트 개

-

벤투의 고백 “이강인, 재능만으로 판단해선 안 됐다”

- 좋아요 개

- 코멘트 개

댓글 0