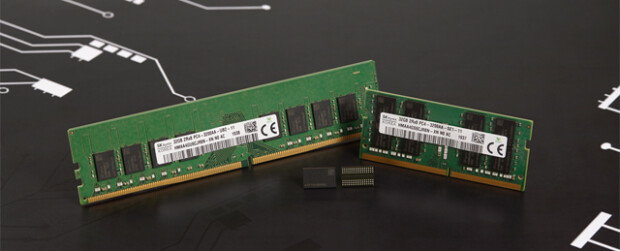

SKハイニックスは、第3世代10ナノ級(1z)微細工程を適用した16Gb(ギガビット)DDR・Dラム(写真)を開発したと、21日明らかにした。今年中に量産準備を終えた後、グローバル半導体の景気回復が予想される来年から、本格的に市場供給に乗り出す計画だ。

SKハイニックスが開発に成功した今回の製品は、第2世代製品(1y)比生産性を約27%高め、極紫外線(EUV)の露光工程がなくても生産可能にして、コスト競争力を大幅に改善したのが特徴だ。10ナノ級Dラムは、工程が細かくなる毎に、第1世代(1x)、第2世代(1y)、第3世代(1z)に分けられる。世代を重ねるほど、生産チップの大きさが小さくなるため、ウェーハー1枚に入るチップの数が増え、生産性が高くなる原理だ。Dラムの標準規格名称であるDDRの場合、データ処理速度に応じてDDR3、DDR4などに区分される。

SKハイニックス側は、「今回の第3世代10ナノ級(1z)Dラムは、単一チップ基準で業界最大容量である16Gbを具現化した」とし、「また、前世代の生産工程では使用しなかった特定物質を適用して、Dラム動作のコア要素である静電容量(Capacitance=電荷を貯蔵できる量)を最大化した」と明らかにした。

Dラム開発事業1zタスクフォース(TF)長のイ・ジョンフン担当は、「第3世代10ナノ級(1z)DDR4・Dラムは、業界最高水準の容量と速度に電力効率まで備えて、高性能・大容量Dラムを求める顧客ニーズの変化に最適な製品だ」とし、「来年から本格的に供給に乗り出し、市場需要に積極的に対応する方針だ」と語った。

徐東一 dong@donga.com